Our current IP in development is a hardware accelerator (HWA) to accelerate cryptographic processing targeted towards RISC-V or ARM cores. Hardware accelerators allow computing systems to accelerate the performance of a particular class of applications by providing hardware support at the algorithmic level.

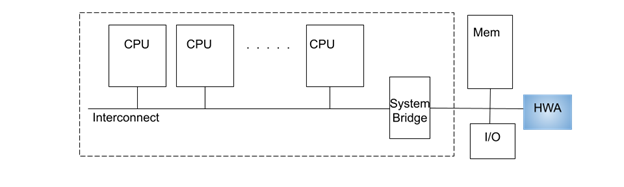

They have been employed in the past in x86 (Intel/AMD) as well as ARM system-on-chip (SOC) designs to accelerate cryptography. The conventional hardware accelerator is attached to a peripheral bus which is relatively far away, in terms of latency, from the main processor core on which software is run. This type of attachment is referred to as loosely attached and is shown in Diagram 1 below.

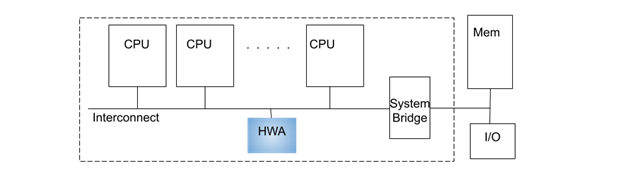

Our design offers a way to attach the hardware accelerator inside the processor cluster with 2 options.

The first is to attach to the interconnect and is referred to as closely attached as shown in Diagram 2.

The second option is to attach inside the main processor core on which software is run and is referred to as tightly attached, as shown in Diagram 3.

The tightly attached option is targeted towards emerging RISC-V cores that do not yet have scalar or vector crypto instruction set extension (ISE) support because the RISC-V crypto ‘K’ extension has not yet been ratified.

With this option, the accelerator state is part of the running thread’s state and can be context switched with the thread. Both options can be used to accelerate the performance of firmware, kernel or application software running a target application.